# CIRCUITOS COMBINACIONAIS - MAPA DE KARNAUGH

Fundação Universidade Federal de Rondônia Núcleo de Ciência e Tecnologia Departamento de Engenharia Elétrica - DEE Disciplina de Sistemas Digitais

#### I. OBJETIVOS

O mapa de Karnaugh é apresentado como uma ferramenta muito útil para simplificação de funções booleanas de até 5 variáveis. Um circuito de decisão de maioria, em que a saída é 1 se, e somente se, a maioria das entradas for 1 é apresentado como exemplo de aplicação.

#### II. INTRODUÇÃO TEÓRICA

#### A. Generalidades

O mapa de Karnaugh é uma forma ordenada para simplificar uma expressão booleana, a qual geralmente nos leva a um circuito com configuração mínima. Pode ser facilmente aplicado em funções envolvendo duas a cinco variáveis. Para seis ou mais variáveis, o método começa a se tornar incômodo, e podemos usar outras técnicas mais elaboradas. Também pode ser usado para determinar se portas duais ou complementares tornarão o circuito mais simples.

#### B. Mintermos e mapas de 2 a 5 variáveis

Qualquer função booleana pode ser escrita na forma canônica disjuntiva ou conjuntiva. A forma canônica disjuntiva é também conhecida como soma de produtos, e é escrita como soma de termos que apresentam sempre todas as variáveis envolvidas. Exemplo: Escrever no forma canônica disjuntiva a função:

$$f(A, B, C) = A(C + \overline{B}) \tag{1}$$

$$f(A, B, C) = A \cdot C + A \cdot \overline{B} \tag{2}$$

$$f(A, B, C) = A \cdot B \cdot C + A \cdot \overline{B} \cdot C + A \cdot \overline{B} \cdot \overline{C} \tag{3}$$

Cada termo é conhecido como produto padrão, produto canônico ou mintermo.

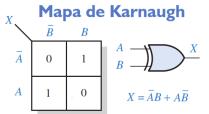

O mapa de Karnaugh é uma forma de representar uma dada função de maneira que cada mintermo mantenha-se vizinho de todos aqueles dos quais difere apenas por uma variável. Assim, os mapas de Karnaugh de 2 a 5 variáveis são indicados nas figuras 1, 2, 3 e 4.

O mapa de Karnaugh de duas variáveis dado pela tabela verdade 1, a seguir, é formado por quatro células  $(2^2 = 4)$  dispostas como mostra a figura.

Tabela I Tabela Verdade de 2 entradas

| ENT   | RAD | SAÍDA |   |

|-------|-----|-------|---|

| $n^o$ | A   | В     | S |

| 0     | 0   | 0     | 0 |

| 1     | 0   | 1     | 1 |

| 2     | 1   | 0     | 1 |

| 3     | 1   | 1     | 0 |

Figura 1. Mapa de Karnaugh de 2 Entradas, e a tabela verdade.

A partir dessa tabela, podemos verificar os seguintes passos para se obter o mapa de Karnaugh e por consequência a simplificação de uma expressão booleana.

- 1º Passo: Obter a tabela verdade do circuito que se quer otimizar;

- 2º Passo: Desenhar as células (retângulos) com todas as combinações possíveis, respeitando a regra de 2<sup>n</sup>, sendo n o número de entradas;

- 3º Passo: Numerar as células conforme as saídas da tabela verdade;

- 4º Passo: Verificar a regra da adjacência, sendo que de uma linha para outra, só poderá haver a variação de uma entrada, e de uma coluna para outra (coluna seguinte) também só poderá haver a variação de uma entrada;

- 5º Passo: Preencher as células conforme as respectivas saídas e fazer o enlace, no enlace verificar as entradas que não se alteram, afim de se obter a operação booleana simplificada.

# C. Exemplo 1: Mapa de Karnaugh com 3 entradas

Vamos fazer um exemplo utilizando o mapa de Karnaugh com 3 entradas. O objetivo é simplificar e expressão booleana para a seguinte tabela verdade.

# 1º Passo: Montar a Tabela Verdade

Nessa parte primeiro devemos montar a tabela, verificando o numero de entradas bem como as saídas correspondentes para cada entrada.

Tabela II Tabela Verdade de 3 entradas

|       | NTRA | SAÍDA |   |   |

|-------|------|-------|---|---|

| $n^o$ | A    | В     | C | S |

| 0     | 0    | 0     | 0 | 1 |

| 1     | 0    | 0     | 1 | 1 |

| 2     | 0    | 1     | 0 | 0 |

| 3     | 0    | 1     | 1 | 0 |

| 4     | 1    | 0     | 0 | 0 |

| 5     | 1    | 0     | 1 | 0 |

| 6     | 1    | 1     | 0 | 1 |

| 7     | 1    | 1     | 1 | 1 |

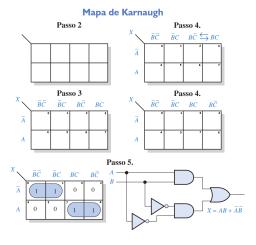

Agora fazendo os passos de 2 a 5, teremos o resultado esperado conforme a figura a baixo

Figura 2. Passos 2, 3, 4 e 5.

## D. Exemplo 2: Mapa de Karnaugh com 4 entradas

Agora iremos fazer um exemplo utilizando o mapa de Karnaugh com 4 entradas. O objetivo é simplificar e expressão booleana para a seguinte tabela verdade.

Tabela III Tabela Verdade de 4 entradas

|       | SAÍDA |   |   |   |   |

|-------|-------|---|---|---|---|

| $n^o$ | A     | В | С | D | S |

| 0     | 0     | 0 | 0 | 0 | 1 |

| 1     | 0     | 0 | 0 | 1 | 0 |

| 2     | 0     | 0 | 1 | 0 | 1 |

| 3     | 0     | 0 | 1 | 1 | 0 |

| 4     | 0     | 1 | 0 | 0 | 1 |

| 5     | 0     | 1 | 0 | 1 | 1 |

| 6     | 0     | 1 | 1 | 0 | 1 |

| 7     | 0     | 1 | 1 | 1 | 0 |

| 8     | 1     | 0 | 0 | 0 | 1 |

| 9     | 1     | 0 | 0 | 1 | 0 |

| 10    | 1     | 0 | 1 | 0 | 1 |

| 11    | 1     | 0 | 1 | 1 | 1 |

| 12    | 1     | 1 | 0 | 0 | 1 |

| 13    | 1     | 1 | 0 | 1 | 1 |

| 14    | 1     | 1 | 1 | 0 | 1 |

| 15    | 1     | 1 | 1 | 1 | 0 |

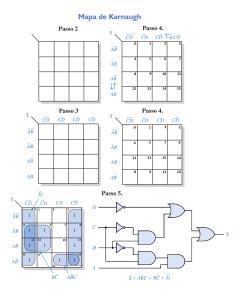

Agora fazendo os passos de 2 a 5, teremos o resultado esperado conforme a figura a baixo

Figura 3. Passos 2, 3, 4 e 5.

## E. Exemplo 3: Mapa de Karnaugh com 5 entradas

Agora iremos fazer um exemplo utilizando o mapa de Karnaugh com 5 entradas. O objetivo é simplificar e expressão booleana para a seguinte tabela verdade.

Tabela IV Tabela Verdade de 5 entradas

|       | ENTRADAS |   |   |   |   |   |

|-------|----------|---|---|---|---|---|

| $n^o$ | A        | В | C | D | Е | S |

| 0     | 0        | 0 | 0 | 0 | 0 | 1 |

| 1     | 0        | 0 | 0 | 0 | 1 | 0 |

| 2     | 0        | 0 | 0 | 1 | 0 | 1 |

| 3     | 0        | 0 | 0 | 1 | 1 | 0 |

| 4     | 0        | 0 | 1 | 0 | 0 | 1 |

| 5     | 0        | 0 | 1 | 0 | 1 | 1 |

| 6     | 0        | 0 | 1 | 1 | 0 | 0 |

| 7     | 0        | 0 | 1 | 1 | 1 | 1 |

| 8     | 0        | 1 | 0 | 0 | 0 | 1 |

| 9     | 0        | 1 | 0 | 0 | 1 | 0 |

| 10    | 0        | 1 | 0 | 1 | 0 | 1 |

| 11    | 0        | 1 | 0 | 1 | 1 | 0 |

| 12    | 0        | 1 | 1 | 0 | 0 | 1 |

| 13    | 0        | 1 | 1 | 0 | 1 | 1 |

| 14    | 0        | 1 | 1 | 1 | 0 | 0 |

| 15    | 0        | 1 | 1 | 1 | 1 | 1 |

| 16    | 1        | 0 | 0 | 0 | 0 | 0 |

| 17    | 1        | 0 | 0 | 0 | 1 | 0 |

| 18    | 1        | 0 | 0 | 1 | 0 | 0 |

| 19    | 1        | 0 | 0 | 1 | 1 | 0 |

| 20    | 1        | 0 | 1 | 0 | 0 | 0 |

| 21    | 1        | 0 | 1 | 0 | 1 | 1 |

| 22    | 1        | 0 | 1 | 1 | 0 | 0 |

| 23    | 1        | 0 | 1 | 1 | 1 | 1 |

| 24    | 1        | 1 | 0 | 0 | 0 | 0 |

| 25    | 1        | 1 | 0 | 0 | 1 | 0 |

| 26    | 1        | 1 | 0 | 1 | 0 | 0 |

| 27    | 1        | 1 | 0 | 1 | 1 | 0 |

| 28    | 1        | 1 | 1 | 0 | 0 | 0 |

| 29    | 1        | 1 | 1 | 0 | 1 | 1 |

| 30    | 1        | 1 | 1 | 1 | 0 | 0 |

| 31    | 1        | 1 | 1 | 1 | 1 | 1 |

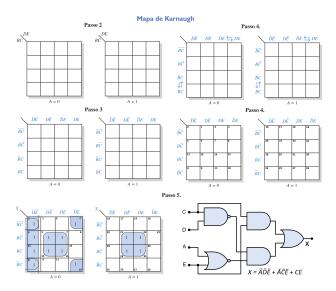

Agora fazendo os passos de 2 a 5, teremos o resultado esperado conforme a figura a baixo

Figura 4. Passos 2, 3, 4 e 5.

## III. MATERIAIS UTILIZADOS

- 01 Gerador de Tensão DC Instrutherm FA 3030;

- 01 Multímetro Digital ICEL MD 6601;

- 03 Resistor de 220  $\Omega$ ;

- 04 Resistor de 510  $\Omega$ ;

- 01 CI 74LS04 Porta Lógica INVERSORA;

- 01 CI 74LS08 Porta Lógica E;

- 01 CI 74LS32 Porta Lógica OU;

- 01 CI 74LS86 Porta Lógica OU-EXCLUSIVO;

- 01 Protoboard;

- 04 Botões Táctil.

#### IV. PARTE EXPERIMENTAL

#### A. Primeira Parte: Mapa K de 3 Variáveis

Faça o Mapa de Karnaugh e monte um circuito lógico representado pela tabela verdade de três variáveis, como mostrado a seguir, somente com portas E e INVERSORA (AND e NOT).

Tabela V Tabela Verdade de 3 entradas

| EN' | ΓRΑΙ | SAÍDA |   |

|-----|------|-------|---|

| Α   | В    | C     | S |

| 0   | 0    | 0     | 1 |

| 0   | 0    | 1     | 0 |

| 0   | 1    | 0     | 1 |

| 0   | 1    | 1     | 1 |

| 1   | 0    | 0     | 1 |

| 1   | 0    | 1     | 0 |

| 1   | 1    | 0     | 0 |

| 1   | 1    | 1     | 0 |

Note que é possível montar esse circuito usando somente 2 CIs. Uma solução possível para implementa-lo é usando o CI 74LS08.

# B. Segunda Parte: Mapa K de 4 Variáveis

Faça o Mapa de Karnaugh e monte um circuito lógico representado pela tabela verdade de quatro variáveis, como

mostrado a seguir, somente com portas E e INVERSORA (AND e NOT).

Tabela VI Tabela Verdade de 4 entradas

| E | ENTR | SAÍDA |   |   |

|---|------|-------|---|---|

| Α | В    | С     | D | S |

| 0 | 0    | 0     | 0 | 1 |

| 0 | 0    | 0     | 1 | 1 |

| 0 | 0    | 1     | 0 | 0 |

| 0 | 0    | 1     | 1 | 0 |

| 0 | 1    | 0     | 0 | 0 |

| 0 | 1    | 0     | 1 | 0 |

| 0 | 1    | 1     | 0 | 0 |

| 0 | 1    | 1     | 1 | 0 |

| 1 | 0    | 0     | 0 | 1 |

| 1 | 0    | 0     | 1 | 1 |

| 1 | 0    | 1     | 0 | 1 |

| 1 | 0    | 1     | 1 | 1 |

| 1 | 1    | 0     | 0 | 1 |

| 1 | 1    | 0     | 1 | 1 |

| 1 | 1    | 1     | 0 | 0 |

| 1 | 1    | 1     | 1 | 0 |

Note que é possível montar esse circuito usando somente três CIs. Uma solução possível para implementa-lo é usando os CIs 74LS08 e 74LS04. Verifique seu funcionamento e veja se está de acordo com a tabela verdade dada.

## C. Terceira Parte: Mapa K de 5 Variáveis

Tabela VII

TABELA VERDADE DE 5 ENTRADAS

|   | EN | SAÍDA |   |   |   |

|---|----|-------|---|---|---|

| Α | В  | С     | D | Е | X |

| 0 | 0  | 0     | 0 | 0 | 1 |

| 0 | 0  | 0     | 0 | 1 | 1 |

| 0 | 0  | 0     | 1 | 0 | 1 |

| 0 | 0  | 0     | 1 | 1 | 0 |

| 0 | 0  | 1     | 0 | 0 | 1 |

| 0 | 0  | 1     | 0 | 1 | 1 |

| 0 | 0  | 1     | 1 | 0 | 1 |

| 0 | 0  | 1     | 1 | 1 | 0 |

| 0 | 1  | 0     | 0 | 0 | 0 |

| 0 | 1  | 0     | 0 | 1 | 1 |

| 0 | 1  | 0     | 1 | 0 | 0 |

| 0 | 1  | 0     | 1 | 1 | 0 |

| 0 | 1  | 1     | 0 | 0 | 1 |

| 0 | 1  | 1     | 0 | 1 | 1 |

| 0 | 1  | 1     | 1 | 0 | 0 |

| 0 | 1  | 1     | 1 | 1 | 0 |

| 1 | 0  | 0     | 0 | 0 | 1 |

| 1 | 0  | 0     | 0 | 1 | 1 |

| 1 | 0  | 0     | 1 | 0 | 1 |

| 1 | 0  | 0     | 1 | 1 | 0 |

| 1 | 0  | 1     | 0 | 0 | 1 |

| 1 | 0  | 1     | 0 | 1 | 0 |

| 1 | 0  | 1     | 1 | 0 | 0 |

| 1 | 0  | 1     | 1 | 1 | 0 |

| 1 | 1  | 0     | 0 | 0 | 0 |

| 1 | 1  | 0     | 0 | 1 | 1 |

| 1 | 1  | 0     | 1 | 0 | 0 |

| 1 | 1  | 0     | 1 | 1 | 1 |

| 1 | 1  | 1     | 0 | 0 | 1 |

| 1 | 1  | 1     | 0 | 1 | 0 |

| 1 | 1  | 1     | 1 | 0 | 1 |

| 1 | 1  | 1     | 1 | 1 | 0 |

Faça o Mapa de Karnaugh e monte um circuito lógico representado pela tabela verdade de cinco variáveis, como mostrado a cima, somente com portas E e INVERSORA (AND e NOT).

Note que é possível montar esse circuito usando somente três CIs. Uma solução possível para implementa-lo é usando os CIs 74LS08 e 74LS04. Verifique seu funcionamento e veja se está de acordo com a tabela verdade dada.

#### REFERÊNCIAS

- SEDRA, Adel S. SMITH, Kenneth C. "Microeletrônica", 5 edição. São Paulo: Pearson Prentice Hall, 2007.

- [2] MALVINO, Albert P. "Eletrônica", Volume 1, 4<sup>a</sup> ed. São Paulo: Makron Books, 1995.

- [3] TOCCI, R.J., WIDMER, N. S., MOSS, G.I. Sistemas Digitais Princípios e Aplicações. Prentice Hall, 10<sup>a</sup> Edição, 2007.

- [4] IDOETA, I.V.; CAPUANO, F.G. Elementos de Eletrônica Digital, 5ª edição. Érica Ltda. 2003

- [5] DE LOURENÇO, A. C. et. al. Circuitos Digitais, 5<sup>a</sup> edição. Érica Ltda. 2004

- [6] FLOYD, T. Digital Fundamentals. A System Approach. Pearson. 2013.

- [7] FLOYD, T. Digital Fundamentals. 10th Edition, Pearson Prentice Hall. 2009.

- [8] LAB. DE ENGENHARIA ELÉTRICA-UNIR. Laboratório de Sistemas Digitais e Microprocessados: site: http://www.labs.eletrica.unir.br/pagina/exibir/646